超大规模集成电路设计 技术、流程与挑战

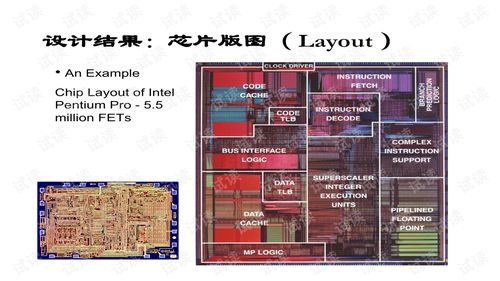

超大规模集成电路(VLSI)设计是电子工程领域的核心技术之一,它涉及在微小的硅片上集成数百万甚至数十亿个晶体管,实现复杂的功能模块,如处理器、存储器和专用集成电路(ASIC)。随着摩尔定律的推进,VLSI 设计在现代电子设备中扮演着至关重要的角色,从智能手机到数据中心,无处不在。

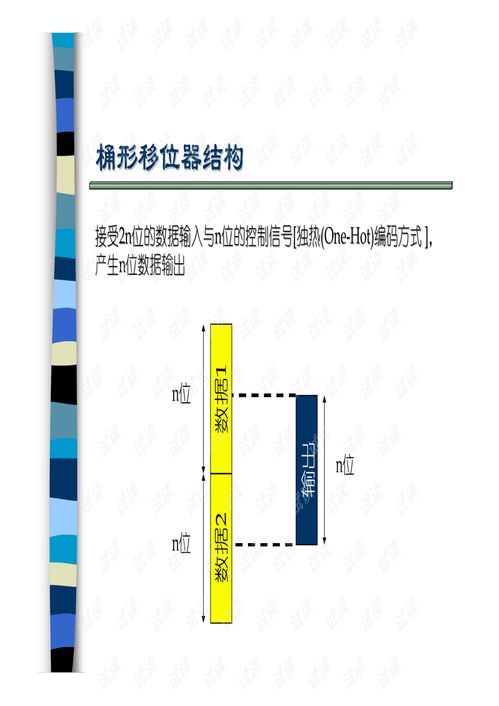

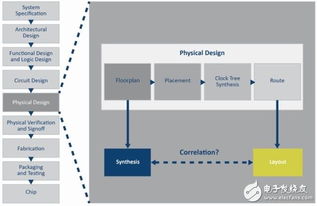

VLSI 设计流程通常包括多个阶段:首先是系统规格定义,明确芯片的功能、性能和功耗要求;接着是架构设计,确定整体结构和模块划分;然后是逻辑设计,使用硬件描述语言(如 Verilog 或 VHDL)实现电路逻辑;之后是物理设计,涉及布局布线,确保电路在硅片上的正确实现;最后是验证和测试,通过仿真和实际测试来保证芯片的可靠性和性能。整个过程需要依赖先进的电子设计自动化(EDA)工具来管理复杂性。

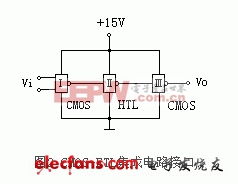

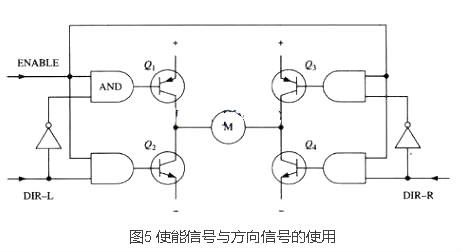

在 VLSI 设计中,关键技术包括 CMOS 工艺、低功耗设计、时序分析和可测试性设计。随着工艺节点不断缩小至纳米级别,设计者面临着诸多挑战,如功耗管理、信号完整性、热效应和制造成本上升。例如,在先进制程下,漏电流和互连延迟成为关键问题,需要采用多电压域、时钟门控等技术来优化。

未来,VLSI 设计正朝着 3D 集成、异构计算和人工智能加速器方向发展,以应对数据爆炸和能效需求。同时,开源 EDA 工具和设计方法的兴起,正在降低设计门槛,推动创新。超大规模集成电路设计不仅是技术进步的引擎,也是推动数字化转型的核心力量,其发展将持续塑造电子产业的未来。

如若转载,请注明出处:http://www.mykmlife.com/product/5.html

更新时间:2026-04-14 18:08:31