集成电路IC后端设计的关键步骤

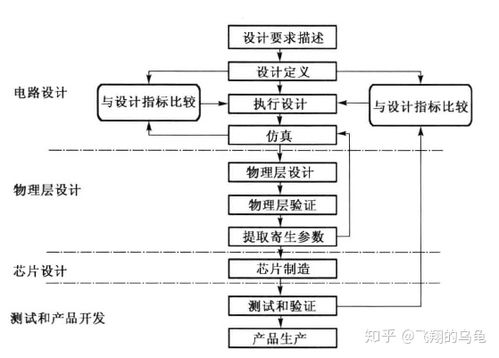

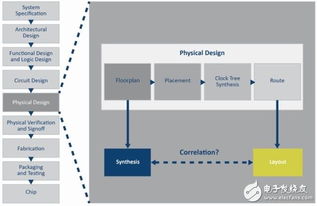

集成电路(IC)后端设计是芯片设计流程中的关键环节,主要负责将前端逻辑设计转化为可制造的物理布局。其核心目标是确保芯片满足时序、功耗和面积等性能指标的实现高良率的制造。后端设计通常包括以下主要步骤:

- 逻辑综合:将前端设计的寄存器传输级(RTL)代码转换为门级网表,同时考虑工艺库、时序约束和功耗要求。综合过程优化电路结构,确保逻辑功能正确并满足初步性能目标。

- 布局规划:确定芯片上各个功能模块的位置和形状,包括电源网络、I/O引脚和硬核的摆放。布局规划直接影响布线拥塞、时序和散热,是后端设计的基础。

- 电源规划:设计电源分布网络(PDN),确保芯片各区域获得稳定供电。这包括电源环、电源带和去耦电容的布局,以降低电压降和电迁移风险。

- 布局:将标准单元和宏模块放置在芯片的特定位置,优化连线长度和时序。布局工具通过算法最小化延迟和面积,同时考虑制造规则。

- 时钟树综合:构建时钟分布网络,确保时钟信号同步到达所有时序单元。时钟树设计需平衡偏斜、功耗和面积,通常采用平衡树结构(如H树或网格)。

- 布线:连接所有单元和模块的物理线路,包括全局布线和详细布线。布线需避免天线效应、串扰和电迁移问题,同时满足设计规则检查(DRC)要求。

- 时序和功耗分析:通过静态时序分析(STA)和功耗模拟验证设计是否满足时序约束和功耗预算。必要时进行优化,如插入缓冲器或调整单元尺寸。

- 物理验证:执行设计规则检查(DRC)、版图与原理图对照(LVS)和电气规则检查(ERC),确保版图符合代工厂的制造标准和电气特性。

- 签核:最终验证设计的所有指标,包括时序、信号完整性和功耗。签核通过后,生成GDSII文件交付制造。

后端设计是IC实现的核心,其成功依赖于EDA工具、工艺库和设计经验的紧密结合。随着工艺节点不断缩小,后端设计面临更多挑战,如寄生效应、热管理和可制造性设计(DFM),需要持续创新和优化。

如若转载,请注明出处:http://www.mykmlife.com/product/46.html

更新时间:2026-04-18 07:45:02