同步时序原理

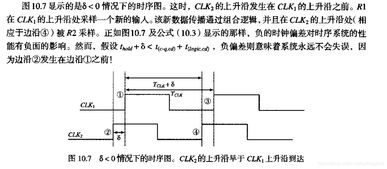

同步时序原理是现代数字集成电路设计的核心概念之一。在《数字集成电路:电路与设计》第二版中,这一原理被详细阐述为:同步时序电路依赖于一个共同的时钟信号来协调所有时序元件的状态变化。时钟信号作为全局参考,确保数据在特定时间点(如时钟边沿)被采样、传输和处理,从而避免竞争条件和时序违规。

同步设计的关键优势在于其简化了时序分析,提高了电路的可靠性和可预测性。例如,在寄存器传输级(RTL)设计中,所有触发器在时钟上升沿或下降沿同步更新状态,使得设计者可以聚焦于功能逻辑,而非复杂的时序问题。同步时序原理有助于减少亚稳态风险,确保系统在高速运行时保持稳定。

同步设计也存在挑战,如时钟偏斜和功耗问题,需要通过时钟树综合和低功耗技术来优化。掌握同步时序原理是集成电路设计师实现高效、稳健数字系统的基石。

如若转载,请注明出处:http://www.mykmlife.com/product/48.html

更新时间:2026-04-14 08:42:20