数字集成电路测试系统的设计 原理、架构与实现

随着现代电子技术的飞速发展,数字集成电路(IC)已成为各类电子设备的核心组成部分。为确保集成电路的可靠性、性能及功能完整性,设计高效、精确的测试系统显得尤为重要。本文将系统阐述数字集成电路测试系统的设计原理、架构组成及实现方法,涵盖测试需求分析、硬件平台搭建、测试向量生成、结果分析与优化等关键环节。

一、测试系统设计概述

数字集成电路测试系统的主要目标是验证芯片在制造过程中是否存在缺陷,并确保其符合设计规范。测试系统通常由测试设备、测试程序、接口适配器和数据分析软件等部分组成。测试过程包括功能测试、参数测试和可靠性测试,需结合自动化技术以提高测试效率与覆盖率。

二、测试系统架构设计

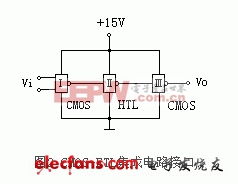

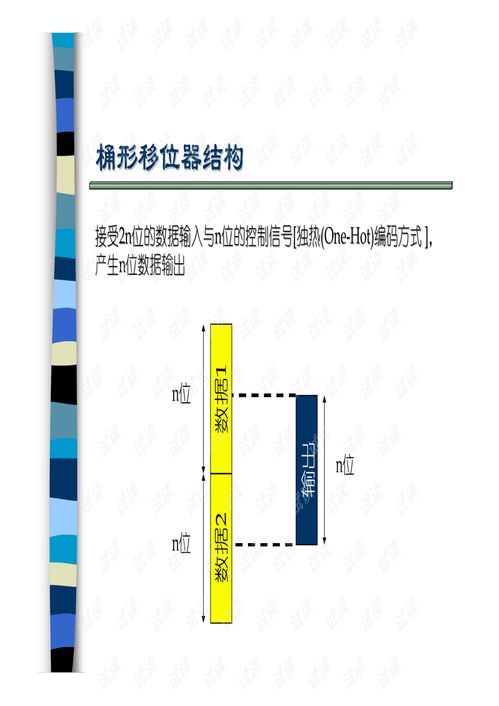

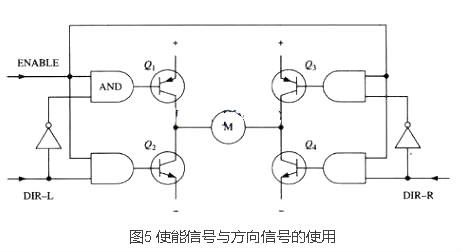

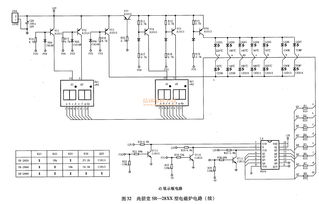

- 硬件平台:测试系统的硬件核心是自动测试设备(ATE),它负责生成测试信号、施加激励并采集被测电路的响应。硬件平台需包括高性能的数字通道、精确的时钟源、电源管理模块以及与被测芯片的接口适配器。可编程逻辑器件(如FPGA)常用于实现灵活的测试逻辑。

- 测试向量生成:测试向量是验证集成电路功能的关键输入序列。常用的生成方法包括确定性测试向量生成和随机测试生成。通过故障模型(如固定故障、延迟故障)分析,设计高效的测试向量以覆盖尽可能多的潜在缺陷。自动化工具如ATPG(自动测试模式生成)可大幅提升向量生成的效率。

- 软件与控制:测试系统软件负责控制硬件、执行测试程序并分析结果。软件架构应包括测试序列编辑器、结果数据库和用户界面。通过集成脚本语言(如Python或TCL),用户可自定义测试流程,实现自动化测试与数据分析。

三、测试流程与实现

测试流程通常分为预测试、核心测试和后测试三个阶段。预测试包括设备校准与连接检查;核心测试阶段施加测试向量并采集响应;后测试则进行数据比较与故障诊断。为实现高精度测试,需考虑信号完整性、时序同步和噪声抑制等问题。

四、挑战与优化策略

数字集成电路测试面临测试时间成本高、故障覆盖率不足等挑战。优化策略包括采用并行测试技术、引入边界扫描(JTAG)标准以简化测试访问,以及利用机器学习算法进行智能故障预测。随着集成电路工艺尺寸的缩小,测试系统需适应低电压、高频信号的测试需求。

五、未来发展趋势

未来数字集成电路测试系统将向更高集成度、智能化和云平台化方向发展。借助人工智能与大数据分析,测试系统可实现自适应测试与预测性维护,提升测试效率与准确性。同时,面向5G、物联网等新兴应用,测试系统需支持多协议、高速接口的验证。

数字集成电路测试系统的设计是一个多学科交叉的工程领域,涉及电子工程、计算机科学和自动化技术。通过合理的架构设计与优化,测试系统能够有效保障集成电路的质量与可靠性,推动电子产业的持续创新。

如若转载,请注明出处:http://www.mykmlife.com/product/14.html

更新时间:2026-04-20 12:46:20