外延片与集成电路设计 从材料到芯片的精密之旅

在现代半导体产业中,外延片的生产与集成电路设计是芯片制造的两大核心支柱,它们共同构成了从基础材料到功能芯片的精密转化过程。外延片作为芯片的物理基底,其质量直接影响最终电路的性能;而集成电路设计则是赋予这片基底以智能与功能的灵魂。

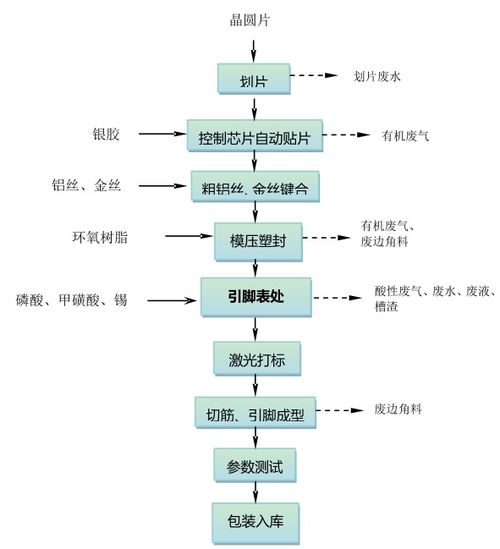

一、外延片:芯片的“地基”

外延片是通过化学气相沉积(CVD)或分子束外延(MBE)等技术,在衬底(如硅、砷化镓)上生长出单晶薄膜的材料。它不仅是集成电路的物理载体,更通过精确控制薄膜的厚度、掺杂浓度和晶体结构,为后续工艺提供理想的基础。外延片的生产资料整理包括:

- 材料选择:根据芯片性能需求(如高频、高压、光电特性)选择衬底与外延层材料组合(如硅上外延硅、碳化硅上外延氮化镓)。

- 工艺参数记录:生长温度、压力、气体流量、掺杂剂浓度等数据直接影响薄膜质量,需系统归档。

- 质量控制数据:薄膜厚度均匀性、缺陷密度、电学参数(如载流子迁移率)的检测报告。

- 设备维护日志:外延生长设备的校准、保养记录,确保工艺稳定性。

这些资料的完整性,是保障外延片批次一致性、提升芯片良率的关键。例如,5G通信芯片需要低缺陷的砷化镓外延片,而新能源汽车功率芯片则依赖高质量碳化硅外延片,其生产资料必须严格对标行业标准。

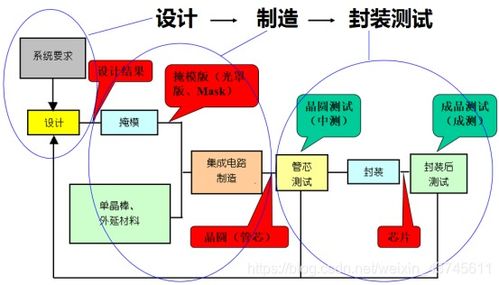

二、集成电路设计:芯片的“蓝图”

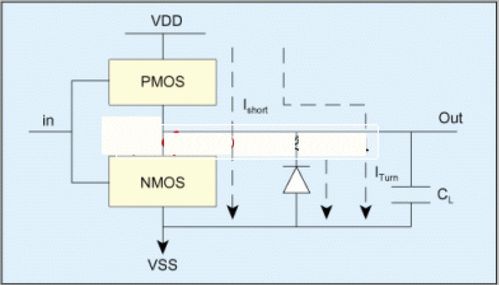

集成电路设计是将电路功能转化为物理布局的过程,涉及系统架构、电路仿真、版图绘制等多个环节。设计资料的核心在于:

- 设计规范文档:包括工艺节点(如7nm、28nm)、功耗、速度、面积等目标参数。

- 电路原理图与HDL代码:使用硬件描述语言(如Verilog)定义逻辑功能,并通过仿真验证正确性。

- 物理版图数据:将电路转换为几何图形,需符合设计规则(DRC)并优化信号完整性。

- 测试与验证报告:功能测试、时序分析、功耗模拟等结果,确保设计可制造且可靠。

以手机处理器为例,设计需在毫米见方的空间内集成数十亿晶体管,外延片的材料特性(如电子迁移率)直接影响晶体管速度,而设计则决定了这些晶体管如何协同工作。

三、协同与优化:资料整合的价值

外延片生产资料与集成电路设计资料并非孤立存在,二者的深度整合能显著提升芯片性能:

- 设计反馈材料:设计阶段发现的速度瓶颈可能通过优化外延片掺杂方案解决。

- 工艺设计套件(PDK):外延片工艺参数被封装为PDK供设计师调用,确保版图符合制造要求。

- 失效分析联动:芯片测试中的缺陷可能追溯至外延片生长异常,需共享数据以快速定位问题。

例如,在第三代半导体氮化镓功率芯片开发中,外延片的界面缺陷控制资料与设计中的电场分布仿真结合,可共同突破高压应用瓶颈。

##

外延片生产资料与集成电路设计资料,如同芯片产业的“左膀右臂”。前者奠定了物理基础,后者勾勒出功能上限。在人工智能、物联网等新兴领域对芯片要求日益严苛的今天,系统化整理并打通这两类资料,不仅是技术管理的需要,更是推动半导体创新的核心动力。只有材料与设计精密耦合,才能让每一片晶圆最终化为智能时代的基石。

如若转载,请注明出处:http://www.mykmlife.com/product/81.html

更新时间:2026-04-14 13:20:56