数字IC设计入门(五) 初识集成电路设计

在数字IC设计的学习旅程中,我们已经掌握了数字逻辑、硬件描述语言等基础知识。现在,让我们正式踏入集成电路(Integrated Circuit, IC)设计的殿堂,了解这一将无数晶体管和电路集成到微小芯片中的宏伟工程。

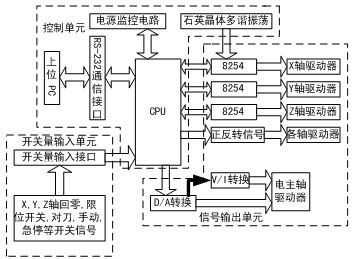

集成电路设计,简而言之,是指将特定功能的电子系统(如处理器、存储器、通信模块等)通过一系列严谨的步骤,最终实现为一块物理硅芯片的过程。它远不止是编写代码或绘制原理图,而是一个融合了系统架构、电路实现、物理布局和工艺制造的复杂系统工程。

核心特点与挑战

1. 高度集成:现代芯片集成了数十亿甚至上百亿个晶体管,如何在极小的面积内实现复杂功能,并保证信号完整性和低功耗,是设计的首要挑战。

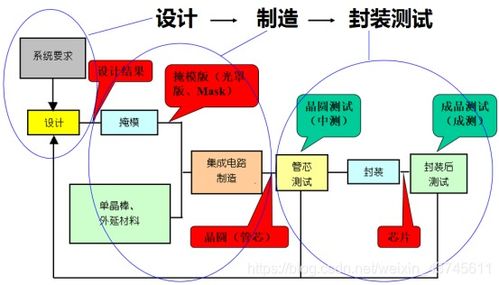

2. 设计流程漫长且环环相扣:从系统规格定义、架构设计、RTL编码、功能验证、逻辑综合、物理设计,到最终的流片制造和测试,每个阶段都至关重要,任何失误都可能导致整个项目失败,成本高昂。

3. 多领域知识融合:设计者需要理解系统架构、数字电路、半导体物理、EDA工具使用,甚至需要对制造工艺有基本认识。

4. 工具依赖性强:整个设计流程高度依赖于电子设计自动化工具链,掌握主流EDA工具是工程师的基本技能。

主要设计流程概述

一个典型的数字IC设计流程主要包括以下几个阶段:

- 规格定义与架构设计:明确芯片要做什么,确定性能、功耗、面积目标,并设计高层次系统架构。

- RTL设计与验证:使用硬件描述语言将架构转化为寄存器传输级代码,并进行充分的功能仿真验证,确保逻辑正确。这是数字设计工程师的核心工作之一。

- 逻辑综合:利用EDA工具,将RTL代码、工艺库和约束文件作为输入,生成门级网表。这一步将行为级描述映射到了实际的标准单元库。

- 物理设计:将门级网表转换成实际的几何图形(布局布线),确定每个晶体管和连线的具体位置。这包括布局规划、时钟树综合、布线、参数提取等步骤,挑战在于满足时序、面积、功耗和信号完整性要求。

- 验证与签核:在流片前进行彻底的验证,包括时序验证、物理验证、功耗分析等,确保设计符合所有规格和制造规则。

- 流片与测试:将最终设计数据交给晶圆厂制造,生产出物理芯片,并进行封装和测试。

给初学者的建议

1. 夯实基础:深入理解数字逻辑、计算机体系结构、Verilog/VHDL语言是根本。

2. 熟悉流程与工具:通过教学项目或开源工具,实践一个从RTL到门级网表的小规模设计流程,建立整体概念。

3. 建立系统思维:始终牢记性能、功耗、面积和成本的权衡,而不仅仅是功能实现。

4. 保持学习:IC技术迭代迅速,新工艺、新架构、新工具不断涌现,持续学习是关键。

初识集成电路设计,我们看到的是一个充满挑战与机遇的精密世界。从宏观架构到微观晶体管,每一层抽象都凝聚着工程师的智慧。在后续的学习中,我们将逐步深入这个流程的每一个关键环节,揭开数字IC设计的神秘面纱。

如若转载,请注明出处:http://www.mykmlife.com/product/90.html

更新时间:2026-04-06 14:10:12