低功耗集成电路设计中的寄存器传输功耗优化策略

在现代集成电路设计中,功耗已成为与性能、面积同等重要的关键设计指标。随着工艺节点不断缩小,动态功耗与漏电功耗的挑战日益严峻,其中寄存器传输级(Register Transfer Level, RTL)的功耗优化是低功耗设计的重要环节。寄存器传输操作频繁,其功耗贡献显著,因此,系统性地解决寄存器传输功耗问题对于实现高效能、低功耗的芯片至关重要。

一、寄存器传输功耗的主要来源

寄存器传输功耗主要源于两个核心部分:

- 组合逻辑切换功耗:数据在寄存器之间通过组合逻辑电路传输时,逻辑门的开关活动会产生动态功耗。这是寄存器传输中主要的动态功耗来源。

- 寄存器本身的操作功耗:包括时钟网络对寄存器时钟端的充电/放电功耗(时钟功耗),以及寄存器数据采样、保持所消耗的功耗。时钟功耗通常是芯片动态功耗的很大一部分。

二、解决寄存器传输功耗的关键技术

针对上述来源,在RTL设计和综合阶段可以采用多层次、多粒度的优化策略。

1. 时钟门控技术

这是降低寄存器相关功耗最有效且广泛应用的技术。其核心思想是:当寄存器组不需要更新数据时,关闭其时钟信号,从而消除不必要的时钟翻转带来的功耗。

- 基于RTL的时钟门控:设计时显式地为功能模块或寄存器块添加使能信号,综合工具可将其自动推断为集成时钟门控单元。

- 自动时钟门控:现代综合工具可以在门级网表中自动识别寄存器的使能条件,并插入时钟门控单元。合理使用时钟门控可大幅降低时钟网络的动态功耗。

2. 操作数隔离

当组合逻辑电路的输入变化不会影响其输出时,该逻辑的开关活动就是多余的。操作数隔离技术通过在逻辑电路的输入端插入门控电路,在输出无需变化时“冻结”输入,阻止信号变化向后续逻辑传播,从而减少不必要的开关活动。这在数据通路、多路选择器等结构中效果显著。

3. 数据编码与总线反演

通过改变数据的表示形式来减少总线上的信号跳变次数。例如,总线反演技术会在传输数据前,判断是否将数据取反后传输能使跳变位数更少,并增加一位标志位来指示是否进行了取反。接收端根据标志位恢复原始数据。这对于高负载、长距离的总线传输尤其有效。

4. 存储器与寄存器文件分区访问

大型的寄存器文件或存储器模块每次访问都会激活整个阵列,功耗巨大。将其划分为多个较小的、可独立使能的区块,每次只访问所需数据所在的区块,可以显著降低激活功耗。这需要在架构设计时就进行规划。

5. 流水线级优化与逻辑重组

通过调整流水线结构、平衡各级延迟,可以降低工作电压或频率,从而平方级地降低动态功耗。对关键路径上的逻辑进行重组和优化,减少逻辑深度和毛刺产生,也能有效降低组合逻辑的切换活动率。

6. 多电压域与电源门控

在系统级,可以为不同性能要求的模块分配不同的工作电压。对于长时间闲置的功能模块,可以完全切断其电源(电源门控),将漏电功耗降至近乎为零。这需要精细的电源管理架构和电平转换、隔离单元的支持。

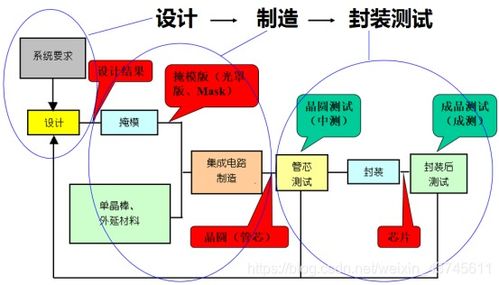

三、设计流程与工具协同

有效的低功耗设计依赖于从架构到物理实现的全程把控:

- 早期评估:在架构和RTL设计阶段,使用功耗预估工具分析不同设计选择的功耗影响。

- RTL设计与综合:采用可综合的低功耗设计描述(如正确使用时钟门控使能信号),并设定综合工具的低功耗优化约束与策略。

- 验证:进行功能验证的也需要进行功耗意图的统一格式(如UPF/CPF)验证,确保低功耗设计在实现中不会引入功能错误。

- 物理实现与签核:在布局布线阶段实施时钟树综合优化、电源网络规划,并在签核阶段进行包含各种工作模式的精确功耗分析。

解决寄存器传输功耗问题是一个系统工程,需要将多种技术有机结合,并在设计流程的各个阶段予以贯彻。从最前端的架构决策,到RTL编码风格,再到后端实现策略,每一个环节都对最终芯片的功耗表现有着深远影响。随着人工智能、物联网等应用对能效比要求的极致化,掌握并灵活运用这些低功耗设计技术,已成为当代集成电路设计师的核心能力之一。

如若转载,请注明出处:http://www.mykmlife.com/product/93.html

更新时间:2026-04-10 10:26:53